Actualités

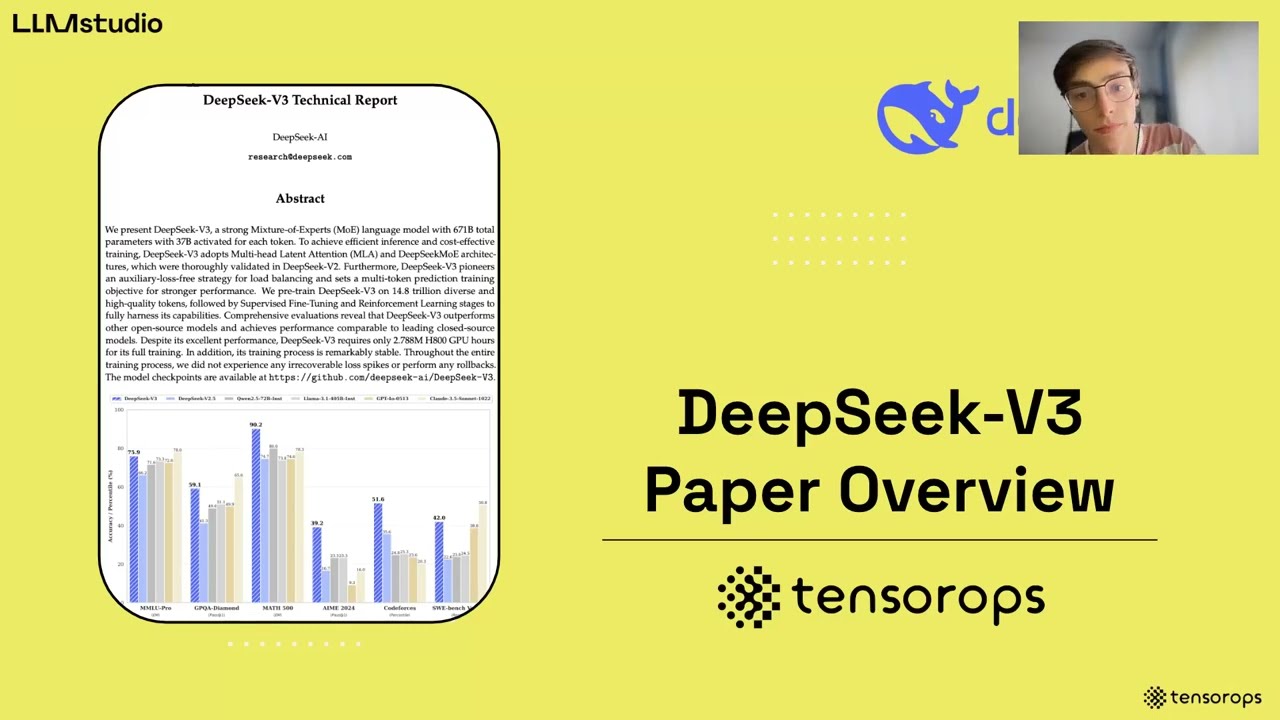

Exciting Announcement: The Upcoming Release of DeepSeek-V3 Paper Reveals Innovative Strategies for Affordable Large Model Training via Hardware-Aware Co-design

Hardware-Aware Co-design for Affordable Training: What the DeepSeek-V3 Paper Signals Next

A fresh technical paper on hardware-aware co-design surrounding DeepSeek-V3 lays out a clear blueprint: smarter model architectures paired with deliberate system engineering can drive massive cost and speed gains without sacrificing quality. The team trained DeepSeek-V3 on 2048 NVIDIA H800 GPUs, facing constrained NVLink bandwidth (~400 GB/s) and policy-limited scale-out—yet still achieved competitive performance by rethinking everything from expert routing to micro-batch scheduling. Instead of treating hardware limits as hard ceilings, the design leans into them: avoiding Tensor Parallelism that amplifies all-reduce pressure, emphasizing Pipeline Parallelism for compute continuity, and accelerating Expert Parallelism with bandwidth-savvy routing. The co-design ethos feels timely as organizations from startups to enterprises eye sustainable AI budgets in 2025.

Consider Orion Labs, a mid-market robotics company piloting a reasoning assistant. Its cluster: four nodes, each with eight H800s and mixed networking. Traditional dense LLM training would choke on bandwidth and memory. By contrast, MoE with node-aware routing and overlapping communication allows Orion to scale within its constraints while preserving latency SLOs. This is the pragmatic difference between aspirational AI and deployable AI.

There’s also a wider market undertone. With OpenAI, Google DeepMind, Anthropic, Meta AI, and Microsoft Research pushing frontier models, the affordability question has become a strategic one. Practitioners operating in PyTorch or TensorFlow, distributing via Hugging Face-backed tooling, now need strategies that harmonize training compute, memory footprints, and interconnect realities. The DeepSeek-V3 report positions co-design as not just an optimization, but an organizational discipline.

Key co-design moves that shift the economics

- 🔧 Node-aware expert routing: keep most expert traffic intra-node to exploit higher NVLink bandwidth and minimize IB contention.

- 🚀 Dual micro-batch overlap: hide communication latency behind compute by design, from day one.

- 🧠 Multi-head Latent Attention (MLA): compress KV to shrink memory needs and keep throughput high.

- 📉 FP8 mixed-precision training: reduce compute costs while preserving quality via extensive calibration.

- 🌐 Multi-Plane Fat-Tree networking: plane-aware routing for robust, low-latency scale-out.

For teams calibrating service throughput against provider caps and user expectations, it’s worth revisiting practical constraints. See this concise analysis of rate limits and scaling when sizing model-backed services that need consistent latency under load.

| Co-design lever 🧩 | Hardware reality ⚙️ | Model/system adaptation 🛠️ | Impact 🎯 |

|---|---|---|---|

| Expert Parallelism | IB vs NVLink bandwidth gap 😬 | Route tokens to experts primarily intra-node ✅ | Less IB congestion, higher effective throughput 🚀 |

| MLA KV compression | HBM growth lags model context 📦 | Compress per-head KV into latent vectors 🧠 | Lower memory, faster cache movement ⚡ |

| FP8 training | Compute and energy budgets 💡 | End-to-end FP8 with careful calibration 🎚️ | Meaningful FLOP savings, quality maintained ✅ |

| Dual micro-batch overlap | Communication stalls ⏱️ | Concurrent compute/comm schedule 🔁 | Better GPU utilization, smoother latency 📈 |

Bottom line: pairing model choices with interconnect-aware scheduling is the difference-maker when hardware is imperfect—which, in production, it always is.

Memory Efficiency with MLA and KV Compression: DeepSeek-V3’s 70 KB/Token Advantage

Memory is the silent bottleneck of modern LLMs. Context windows grow, prompts get longer, and caching explodes. DeepSeek-V3 reframes the problem by making KV caching cheaper at the source: Multi-head Latent Attention (MLA) compresses the key-value representations from all heads into a joint latent space learned with the model. At inference time, the system caches only the latent vector, not every head’s full KV, unlocking dramatic savings.

The magnitude matters. Compared with large dense baselines, the paper highlights a per-token KV footprint of ~70 KB for DeepSeek-V3. For perspective, comparable figures cited for big dense models can reach ~327 KB and ~516 KB per token. On long sequences, that delta compounds into millions of KB saved per active batch, translating to fewer cache swaps, more resident batches, and higher sustained TPS.

Compression alone doesn’t tell the full story. The team also discusses options like GQA/MQA (shared KV), windowed caching, and quantization compression. The theme: be selective about what is remembered and at what precision. Every byte spared from HBM is capacity that can be redeployed to either longer contexts or more concurrent requests.

How teams can apply MLA-style thinking beyond DeepSeek

- 🧮 Quantify per-token KV costs: measure memory per-token across your stack to expose hidden headroom.

- 🔬 Pilot latent-KV variants: start with synthetic workloads to validate loss curves and latency trade-offs.

- 🧰 Combine techniques: layer MLA with windowed KV or GQA to pursue multiplicative gains.

- 🧵 Stage-aware caching: separate prefill and decode caches to prioritize hot-path latency.

- 📊 Observe real traffic: production prompts differ from benchmarks—measure, don’t assume.

Teams that run inference under external throttling will recognize the operational link: if the service is rate-limited, squeezing more useful work into each token budget helps. For context on how rate caps shape practical throughput, browse this deep dive on API rate limits and how they interact with batching, KV eviction, and latency SLOs.

| Model 🧠 | KV per token (approx) 💾 | Memory techniques used 🧪 | Practical effect 🚀 |

|---|---|---|---|

| DeepSeek-V3 | ~70 KB ✅ | MLA + routing-aware scheduling 🔁 | Higher batch residency, steadier TPS 📈 |

| Qwen-2.5 72B | ~327 KB 😮 | Dense attention, classic KV 📦 | Heavier HBM use, earlier cache pressure ⏳ |

| LLaMA-3.1 405B | ~516 KB 😵💫 | Dense attention, classic KV 📦 | Aggressive memory needs at long context 🧱 |

Curious how others present the memory–latency trade across long-context prompts? A quick search often surfaces demos and talks breaking down KV scaling under load.

One rhetorical question to carry into design reviews: if memory were your scarcest resource, how would you reshape attention? DeepSeek’s answer—compress first, cache less—delivers a strong template.

Sparse MoE Economics, FP8 Training, and Local Inference: The DeepSeekMoE Playbook

The reason MoE feels inevitable in 2025 is simple: sparse activation trims compute without shrinking total parameter capacity. DeepSeek-V3 exemplifies this: ~671B total parameters with ~37B active per token. That asymmetry enables a model with vast representational breadth while keeping per-token FLOPs manageable. In the report’s comparisons, dense peers consume significantly higher compute because they activate everything on every token, regardless of task specificity.

This matters beyond cloud training bills. Sparse computation scales down to personal devices and edge servers. DeepSeek’s prior 236B-class model demonstrated that ~21B active parameters during inference can yield ~20+ tokens/sec on a capable AI SoC-equipped PC—a performance tier that dense models of similar scale struggle to touch locally. For Orion Labs, this means a field engineer can run a specialized assistant offline during a warehouse audit, then sync insights later.

The paper also underscores FP8 mixed-precision training—a notable first at this scale for a public model—leveraging NVIDIA’s Transformer Engine with rigorous calibration and algorithm–infra collaboration. The payoff is tangible: less power, fewer FLOPs, and tight quality curves. The team doubled down with low-precision LogFMT-nBit experiments for communication, trimming bytes on the wire during expert-parallel shuffles. The combined effect: fewer bottlenecks from memory to network to compute.

Compute budget comparisons that clarify the trade

- ⚖️ MoE vs. dense: activate only what’s needed per token; keep the rest idle to save FLOPs.

- 🪫 FP8 where it counts: use lower precision end-to-end with guardrails to maintain stability.

- 📶 Compressed networking: schedule tokens with FP8 metadata to halve comm volume versus BF16.

- 🧩 Routing that respects topology: constrain expert fan-out to reduce cross-node chatter.

- 🧭 Local-first inference: push select workloads to user devices for privacy and responsiveness.

| Model/Mode 🔬 | Active params/token 🧠 | Approx compute per token 🧮 | Implication 📌 |

|---|---|---|---|

| DeepSeek-V3 (MoE) | ~37B ✅ | ~250 GFLOPs ⚡ | Cost-efficient scale with strong quality 🚀 |

| Qwen2.5–72B (dense) | 72B 😮 | ~394 GFLOPs 🧯 | Higher training cost, tougher to scale 📉 |

| LLaMA-3.1–405B (dense) | 405B 😵 | ~2448 GFLOPs 🧨 | Very high cost; requires premium interconnect 💸 |

If your service also contends with API ceilings, moored by provider rules or internal fairness policies, the MoE + FP8 playbook complements ops discipline. For a quick refresher on planning under external constraints, review this context on model deployment constraints and how smart batching plus sparse activation stabilizes user-facing latency.

Another practical angle: aligning this approach with the broader ecosystem. OpenAI and Anthropic continue to explore reasoning-centric scaling; Google DeepMind and Meta AI have open and closed tracks. Regardless of stack—PyTorch or TensorFlow—the lesson holds: sparse where possible, compressed where safe, topology-aware whenever bandwidth is finite.

Throughput, Latency, and Overlap: From Dual Micro-Batches to IBGDA

Training and serving at scale is a story of both throughput and tail latency. DeepSeek-V3 is engineered to hit both. The architecture uses dual micro-batch overlap out of the gate, staging compute so that MLA and MoE phases interleave their scheduling and communication with ongoing kernel execution. It’s a pipeline that acts like a continuously spinning flywheel, designed to keep GPUs saturated even as all-to-all traffic ebbs and flows.

On the serving side, prefill and decode are split. Batch-heavy prefill rides larger expert-parallel groups; latency-sensitive decode receives smaller, nimble groups. That separation matters under turbulence—queue spikes, mixed request sizes, and uneven prompt structures. Meanwhile, IBGDA (InfiniBand GPUDirect Async) removes CPU proxy overhead, letting GPUs write RDMA doorbells directly. For traffic patterns with many small packets—common in all-to-all—this removes a stubborn source of jitter.

Networking is the canvas. The team deployed a Multi-Plane Fat-Tree (MPFT) to increase robustness and balance. Each GPU–NIC path lands on a separate plane; workloads get fault isolation and improved load spreading. While the deployment was bounded by policy limits, performance measured on thousands of GPUs indicates MPFT can match single-plane multi-rail in all-to-all throughput, with operational wins in resilience.

Operational tactics to keep latency honest

- ⏱️ Decode isolation: reserve smaller, fast lanes for token-by-token decoding.

- 🔄 Pipelined overlap: schedule micro-batches so every comm phase is hidden behind another compute phase.

- 🧵 IBGDA everywhere: let GPUs manage the control plane to avoid CPU bottlenecks.

- 🛰️ Plane-aware routing: distribute flows across MPFT planes to dampen hotspots.

- 📈 Token output speed: prioritize tokens/sec for reasoning loops and RL workflows.

| Technique ⚙️ | What it targets 🎯 | Why it helps 💡 | Observed effect 📊 |

|---|---|---|---|

| Dual micro-batch | Comm/computation stalls 🧊 | Overlaps all-to-all with kernels 🔁 | Smoother utilization, fewer gaps 🚀 |

| Prefill/decode split | Tail latency spikes 🐢 | Dedicated EP groups by SLA 🛤️ | Stable p95/p99 under load ✅ |

| IBGDA | CPU proxy overhead 🖥️ | GPU writes doorbells directly 🔔 | Lower microsecond jitter ⏱️ |

| MPFT | Plane congestion 🚦 | Multi-plane distribution 🌐 | Robustness without throughput loss 🛡️ |

If your service planning requires aligning user-visible latency to platform limits, operational guidance like this operational insights on throughput caps can connect the dots between algorithmic choices and production SLOs.

In short, overlap and topology awareness are the quiet superpowers of modern inference stacks.

Future Directions: Unifying Scale-Up and Scale-Out for the Next Wave of Affordable AI

Even with careful routing, the gulf between NVLink (intra-node) and InfiniBand (inter-node) makes certain kernels harder than they should be. The DeepSeek-V3 paper points to a pragmatic North Star: converge scale-up and scale-out with a unified communication fabric and dedicated co-processors for message handling and forwarding. By relieving GPU SMs from packet orchestration, software stacks simplify and more of the chip returns to math.

The team also flags dynamic bandwidth allocation across NVLink and PCIe as a must-have. When KV fetches from CPU RAM collide with EP traffic, stalls and spikes appear. Smarter I/O chiplets, native prioritization, and a tighter CPU–GPU interconnect would reduce contention. Emerging standards like UEC and UALink, plus “unified bus” ideas, hint at where vendors are heading—toward fabrics that treat locality and distribution as one problem.

Networking intelligence is overdue. Think co-packaged optics, lossless mechanisms tuned for all-to-all, and adaptive routing that actually understands MoE flows. Further out, the paper spotlights memory-centric architectures—DRAM stacking, wafer-scale integration, and on-network compression/compute—that attack the memory bandwidth crisis feeding long-context and chain-of-thought models. Robustness also gets focus: silent data corruption checks, faster recovery, and non-stop training become table stakes at multi-thousand GPU scale.

A practical roadmap for teams and vendors

- 🧭 Short term: bake node-aware routing and FP8 paths into your PyTorch/TensorFlow stacks; formalize prefill/decode separation.

- 🏗️ Mid term: adopt MPFT or multi-rail analogs; push IBGDA-like features across accelerator fleets.

- 🚦 Traffic control: experiment with prioritization for KV migrations; monitor plane-level utilization in real time.

- 🧪 New data types: pilot LogFMT-nBit for control-plane metadata to reduce chatter.

- 🧱 Long term: advocate for unified fabrics, comm co-processors, and memory-centric designs with vendors.

| Direction 🚀 | What changes in hardware 🧩 | Software payoff 🧠 | Who benefits 👫 |

|---|---|---|---|

| Unified fabric | NVLink ↔ IB co-processing 🔀 | Simpler kernels; fewer stalls ⚡ | Clouds, on-prem clusters, startups 🌱 |

| Bandwidth control | Dynamic NVLink/PCIe arbitration 🎛️ | Smoother tail latency 🎯 | Realtime and enterprise apps 🏢 |

| Memory-centric | DRAM stacking, wafer-scale 🧱 | Longer context without swaps 📚 | Reasoning and agent stacks 🤖 |

| Intelligent networks | Co-packaged optics, adaptive routing 🛰️ | Stable all-to-all at scale 🌐 | MoE and multimodal training 🎨 |

To ground these ideas, Orion Labs rethinks its roadmap: adopt multi-plane networking today, push for unified fabrics in the next hardware refresh, and upgrade its Hugging Face-based deployment to support FP8 inference kernels where safe. Meanwhile, strategy teams triangulate against industry leaders—OpenAI, Google DeepMind, Anthropic, Meta AI—to ensure competitive capability without runaway cost. If external platforms impose caps, planning ahead with this guide to navigating rate-limited systems helps right-size concurrency, batching, and token budgets before go-live.

Finally, the enduring insight: the future of affordable AI lies in hardware-aware model design and model-aware hardware design meeting in the middle.

For completeness, product teams can also factor user-facing stability: when providers enforce request ceilings, a planning primer like this practical notes on service throttling will keep promises aligned with infrastructure realities.

Network Designs That Scale: MPFT vs. MRFT, IB vs. RoCE, and Where Latency Still Hides

Underneath MoE’s elegance is a relentless all-to-all requirement. DeepSeek’s measured take compares MPFT (Multi-Plane Fat-Tree) against MRFT (Multi-Rail Fat-Tree) and drills into IB vs. RoCE latency behavior. The field-tested conclusion: MPFT can match MRFT’s all-to-all performance while buying fault isolation and easier troubleshooting. InfiniBand reliably posts lower microsecond latency than RoCE for the current generation—useful when decoding work is hypersensitive to jitter.

The report notes practical constraints: ideal NIC-side port bonding and native out-of-order reassembly across planes were not fully available in some deployments, but newer silicon (e.g., ConnectX-8) moves the needle with multi-plane support. As those features land, the two-layer fat-tree becomes even more attractive: scalable, cost-aware, and low-latency enough for MoE’s hungry patterns. In parallel, IBGDA demonstrates that removing the CPU from the control path isn’t a nice-to-have but a must-do.

Decisions that shape real system behavior

- 🧭 Pick IB for latency-critical paths: keep RoCE for storage or cost-sensitive tiers.

- 🛤️ Adopt MPFT for resilience: isolate planes to localize faults and balance load.

- 🧮 Right-size EP groups: smaller for decode, larger for prefill, tuned per workload.

- 🧰 Enable IBGDA: push WRs from GPU, remove CPU mediators.

- 🛰️ Watch for multi-plane features in new NICs: port bonding and ordering semantics are difference-makers.

| Choice 🧩 | Pros ✅ | Cons ⚠️ | Best for 🏁 |

|---|---|---|---|

| MPFT | Fault isolation, load balance, similar throughput 🚀 | Requires plane-aware ops and tooling 🧭 | MoE training at multi-thousand GPU scale 🧠 |

| MRFT | Mature tooling, wide support 🛠️ | Less isolation; single-plane hotspots 🔥 | Classic data-parallel workloads 🧪 |

| IB | Lower latency, strong RDMA stack ⏱️ | Cost and vendor lock-in risks 💸 | Decode, all-to-all critical sections 🎯 |

| RoCE | Commodity friendliness, cost options 🧾 | Higher latency, scalability caveats 🧯 | Storage, non-critical comms 📦 |

As customer-facing stacks must reconcile infra with product realities, the ops plan should include surface-level safeguards. A quick refresher—this analysis of rate limits and scaling—helps calibrate concurrency, token budgets, and shaping rules before rollout. That way, when the model gets smarter, the experience remains smooth.

Closing insight: the network is now part of the model. Treat it with the same rigor as loss curves and eval suites.

What makes FP8 training in DeepSeek-V3 notable for affordability?

It is one of the first publicly documented large-scale MoE trainings using end-to-end FP8 on production hardware. The approach, enabled by NVIDIA’s Transformer Engine and careful calibration, reduces compute and energy costs while maintaining quality, which directly lowers training budgets and widens accessibility.

How does Multi-head Latent Attention reduce memory pressure?

MLA compresses per-head key–value tensors into a shared latent representation learned jointly with the model. During inference, only the latent KV is cached, dropping per-token memory to about 70 KB in DeepSeek-V3—far lower than many dense peers—allowing more concurrent requests and longer contexts.

Why is node-aware expert routing a big deal?

Expert Parallelism can overwhelm inter-node links. By grouping experts per node and routing tokens to minimize cross-node hops, DeepSeek-V3 leverages higher intra-node bandwidth, cuts IB contention, and sustains throughput under real workloads.

Is MPFT better than MRFT for all deployments?

Not always. MPFT offers strong fault isolation and plane-wise balancing with similar all-to-all throughput in tests, but it requires plane-aware operations and hardware support. For some environments, MRFT’s maturity and tooling are still compelling.

How do service rate limits influence architecture decisions?

When platforms cap request or token throughput, teams must increase useful work per token and smooth latency. Techniques like MLA, prefill/decode separation, and sparse MoE help achieve steady performance within caps. For a primer, see this resource on rate caps and throughput planning: https://chat-gpt-5.ai/chatgpt-rate-limits-insights.

Jordan has a knack for turning dense whitepapers into compelling stories. Whether he’s testing a new OpenAI release or interviewing industry insiders, his energy jumps off the page—and makes complex tech feel fresh and relevant.

-

Open Ai2 months ago

Open Ai2 months agoHow to Effortlessly Access Your Archived Conversations on ChatGPT in 2025

-

Open Ai2 months ago

Open Ai2 months agoA Comprehensive Guide to Sharing Your ChatGPT Conversations: 2025 Edition

-

Tools1 month ago

Tools1 month agoHow to download and use open subtitles for movies and TV in 2025

-

Actualités1 month ago

Actualités1 month agoOntario Man Claims ChatGPT Prompted Psychosis During ‘World-Saving’ Quest

-

Ai models2 months ago

Ai models2 months agoMIT Researchers Introduce ‘SEAL’: A Game-Changer in the Evolution of Self-Enhancing AI

-

Actualités2 months ago

Actualités2 months agoOpenAI Reports That Hundreds of Thousands of ChatGPT Users May Experience Symptoms of Manic or Psychotic Episodes Weekly